先进逻辑技术解决方案

先进逻辑技术的发展(FinFET 及更高级技术)需要探索新材料和晶体管结构,以实现最佳功率、面积、成本和制造良率 。在先进技术的发展中,一个主要挑战是尽早确定最佳架构,同时涵盖所有可能的器件和工艺技术选项。

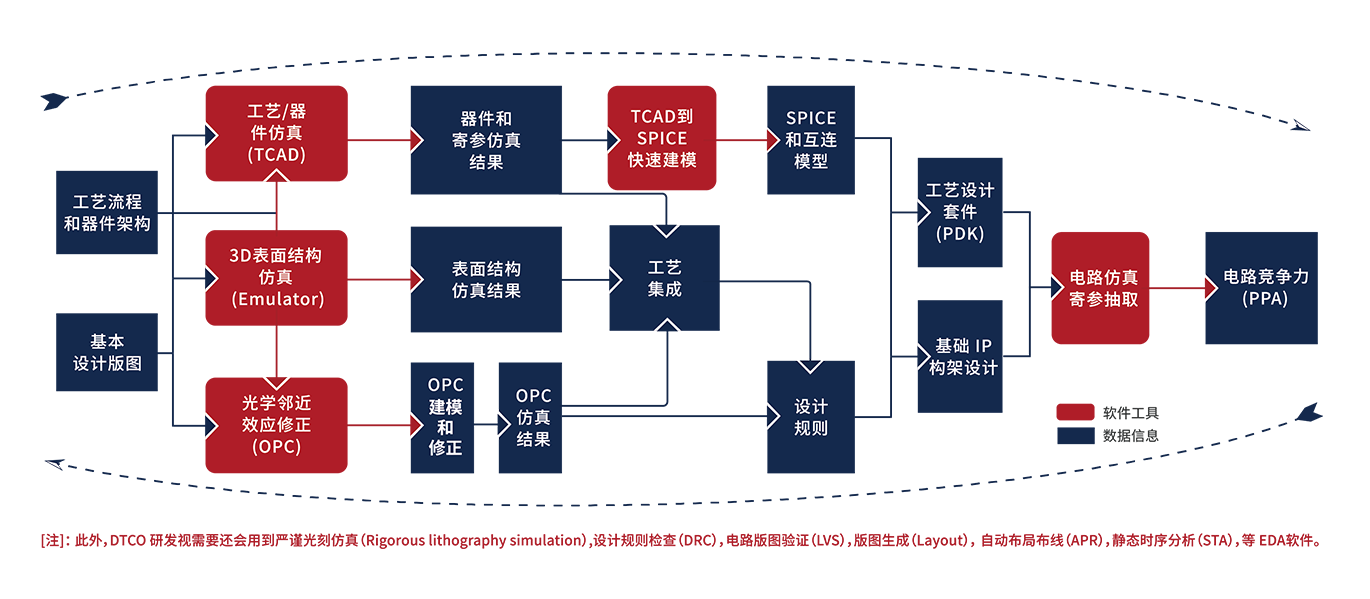

我们的高保真工艺、器件和光刻模拟器套件可在任何晶圆可用之前对器件和工艺选项进行评估。设计连接工具可为器件生成基于 TCAD 的紧凑模型,为电路区块生成寄生 RC 网表,并可进一步分析性能、功耗、面积、成本和制造良率指标。

在先进逻辑技术领域的不断发展中,DTCO(Design Technology Co-Optimization,设计工艺协同优化)扮演着至关重要的角色。特别是随着FinFET及更高级技术的崛起,对于新材料和晶体管结构的探索变得愈发迫切,以寻求在功率、面积、成本和制造良率之间的最佳平衡点。然而,在推动这些先进技术向前发展的过程中,一个不容忽视的挑战在于如何尽早确定最佳的架构方案,同时能够全面覆盖所有可能的器件和工艺技术选项。

为了应对这一挑战,我们引入了高保真度的工艺、器件和光刻模拟器套件。这一创新性的工具套件能够在任何晶圆实际可用之前,对器件和工艺的各种选项进行精确评估。这不仅有助于我们提前识别出潜在的问题和瓶颈,更能在设计初期就进行有针对性的优化,从而大幅提升最终产品的性能表现。

此外,我们还利用设计连接工具生成基于TCAD(Technology Computer Aided Design,计算机辅助技术设计)的紧凑模型。这些模型能够准确地反映设备和电路块的寄生RC网络列表,进而为性能、功耗、面积、成本和制造良率等指标提供深入的分析依据。通过这种方法,我们能够在设计过程中及时发现并修正潜在的缺陷,确保最终产品的各项指标均能达到预期目标。

综上所述,我们的高保真度工艺、器件和光刻模拟器套件以及基于TCAD的紧凑模型生成工具,为先进逻辑技术中的DTCO提供了强有力的支持。它们不仅有助于我们实现器件和技术的协同优化,更能推动整个先进逻辑技术领域的持续进步和发展。

背面供电网络(BSPDN):设计—工艺协同优化案例

背景与目标

在先进逻辑技术中,FinFET技术是当前主流的晶体管架构。然而,在晶体管之外,由金属导线构成的供电网络也是决定电路性能的重要因素。随着技术节点的不断缩小,传统正面供电网络(FSPDN)面临着诸多挑战,如电源线电阻增加导致的IR drop问题、布线空间受限导致的面积效率低下等。背面供电网络(BSPDN)作为一种新兴的解决方案,通过将电源线从正面转移到背面,能够有效缓解上述问题。

背面供电网络有多种技术方案,每个技术方案在各个步骤又有多种工艺选项和参数。DTCO方法论在上述技术路线选择,选项和参数优化的过程中扮演着至关重要的角色。工程师通过器件与工艺的协同优化,实现最佳的性能、功耗、面积和成本平衡。

解决方案

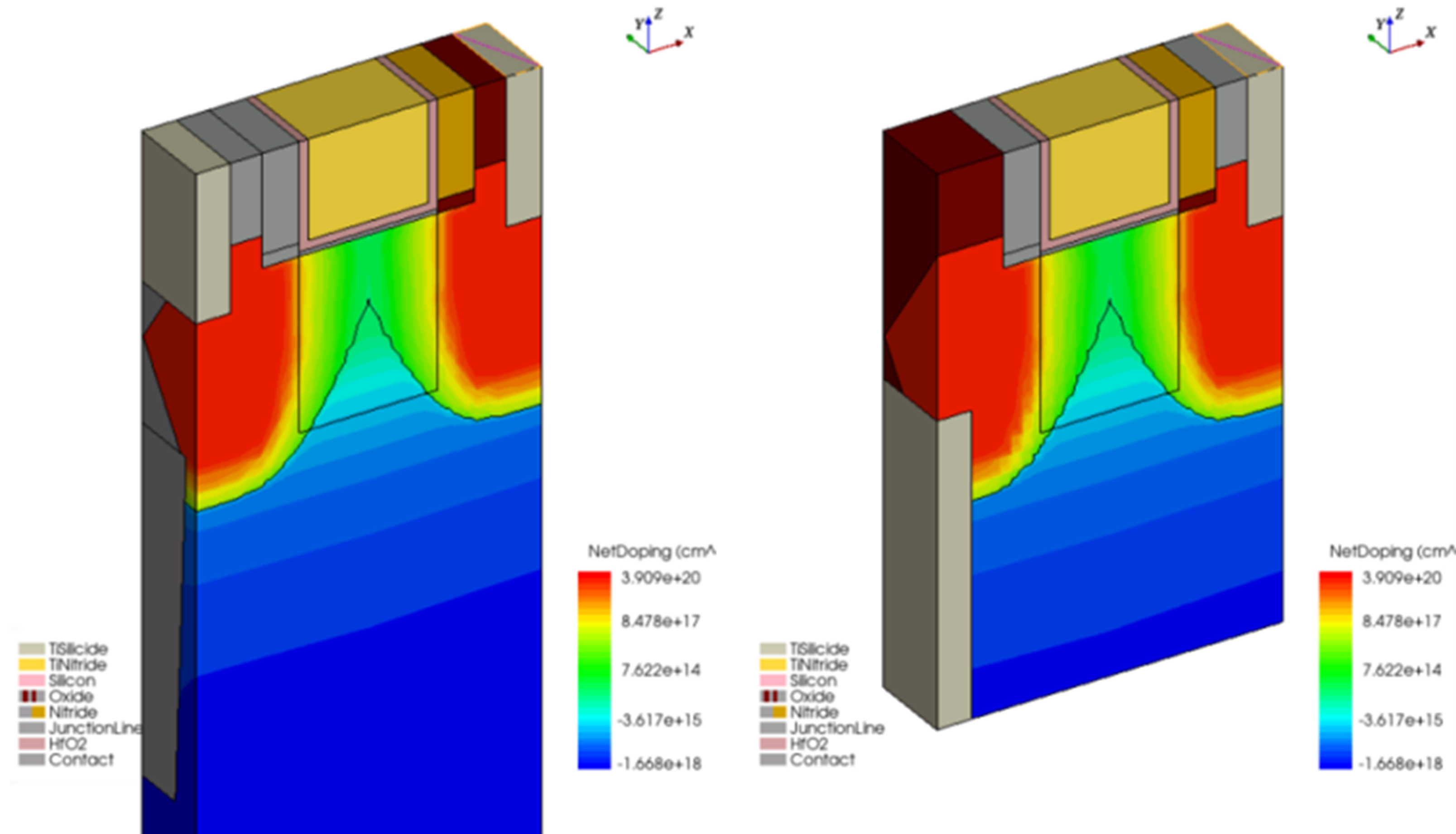

通过工艺仿真(Mozz-Process)得到传统的正面供电FinFET器件结构(下图左),和背面金属接触孔(BSC)的FinFET器件结构(下图右)。

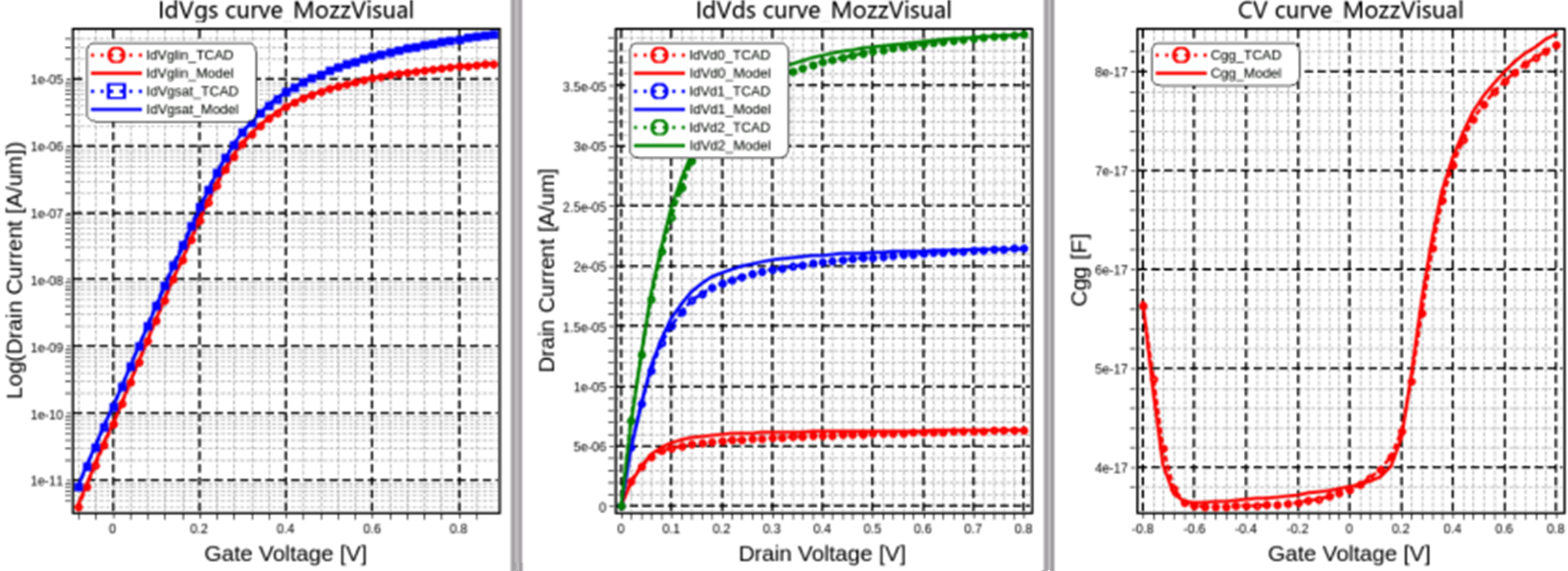

通过器件仿真(Mozz-Device)得到这两种结构的IV/CV特性曲线,并用Mozz-Extract得到相应的紧凑型模型。

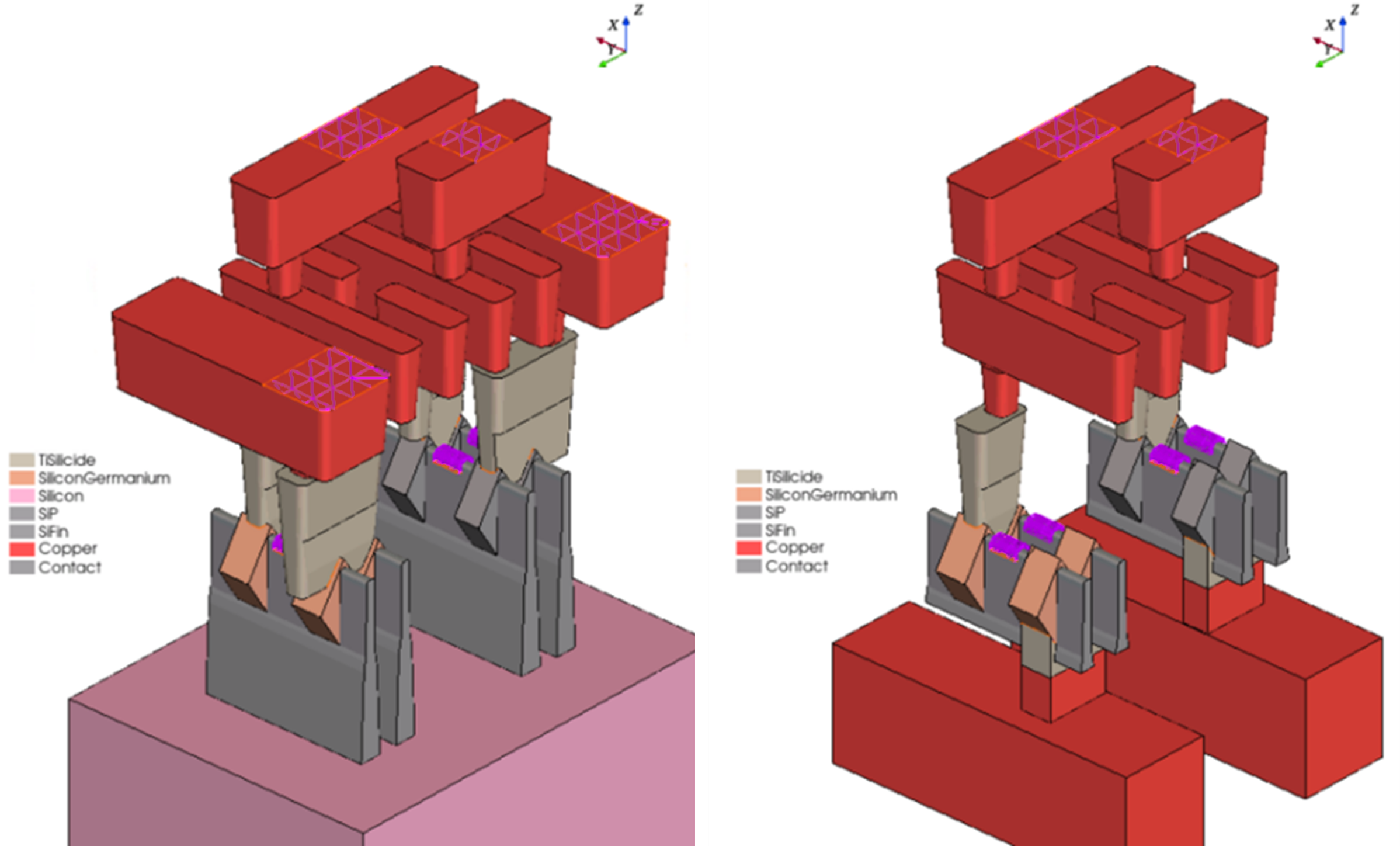

通过形貌仿真(Mozz-ProcEmu)或结构仿真(Mozz-Structure)搭建一个正面供电反向器的标准单元结构(下图左),和一个背面供电的标准单元结构(下图右),并用Mozz-RCEx提取相应的寄生电阻电容网表。

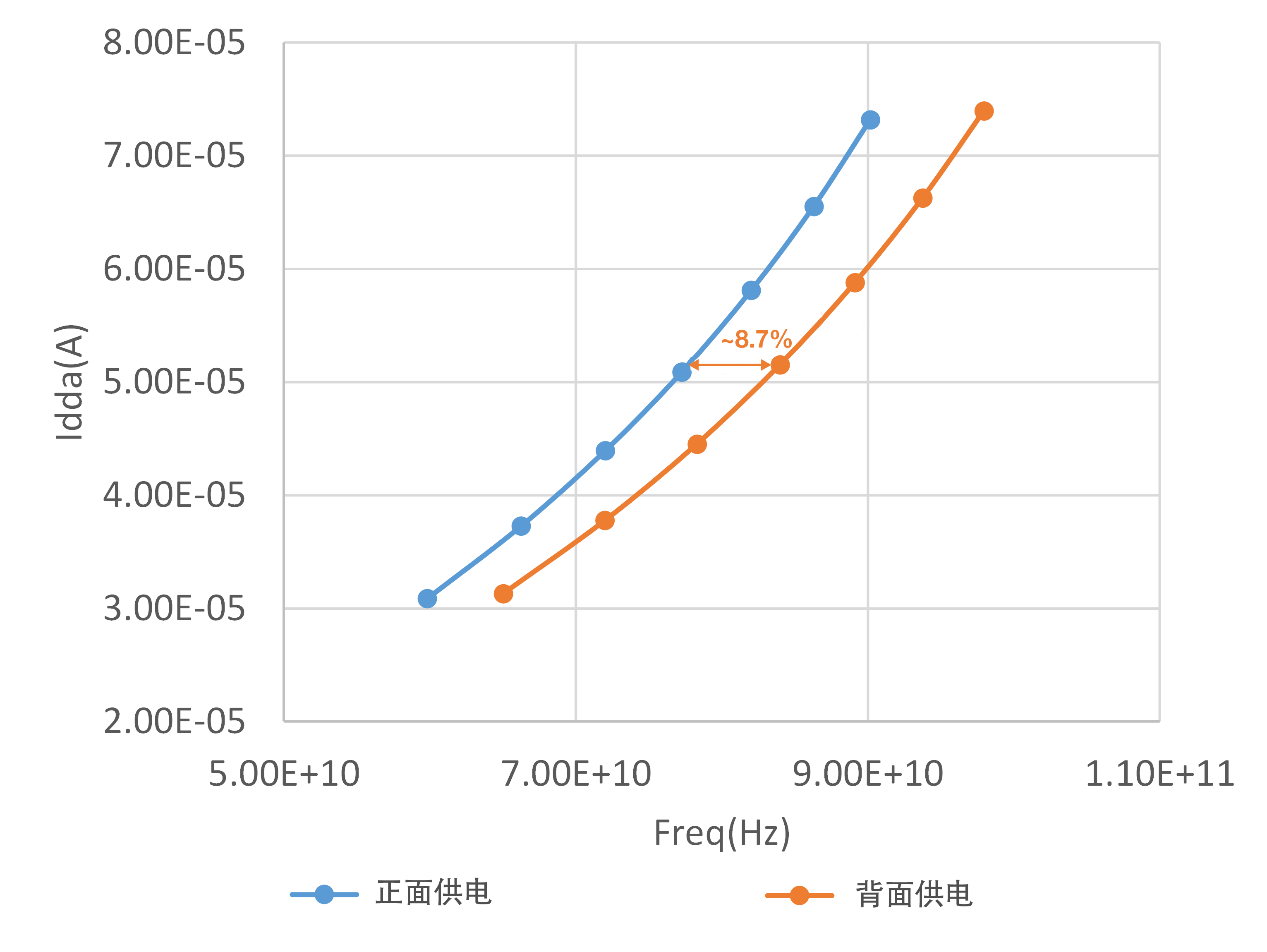

通过SPICE电路级仿真,得到相应的环形振荡器(RO)的仿真结果,该结果中背面供电的RO性能有了显著的提升。

案例总结

通过以上DTCO方法,结合FinFET器件的结构优化和背面工艺的集成,可以实现背面供电网络的高效应用。通过精确的模拟和优化,不仅能提升器件的性能和效率,还能降低功耗和成本,为先进逻辑技术的发展提供了有力支持。

国产EDA技术先驱 | 培风图南半导体

国产EDA技术先驱 | 培风图南半导体