Y-CHIP测试芯片设计平台

设计背景

在集成电路(IC)产线导入初期,良率通常经历从0%逐步提升至100%的过程。为加快问题发现与解决,需要借助测试芯片对工艺相关的关键模块进行验证。Y-CHIP设计正是为满足这一阶段的工艺测试和设计验证需求而提出。

设计策略

Y-CHIP的设计遵循以下关键原则:

- 多样化规则与版图方案覆盖:集成不同的设计规则与版图布局,以支持早期工艺阶段的对比分析,选出最优设计策略;

- OPC方案多样化验证:采用多种光学邻近修正(OPC)方案,通过测试选出最佳工艺组合;

- 基于真实电路构建测试平台:所有测试内容基于具体电路单元构建,如标准单元库、IO、SRAM、关键IP模块等;

- 全覆盖标准单元与IO单元:涵盖完整标准单元库与所有IO电路,支持mini-PAD设计,以确保可用探针直接进行功能测试;

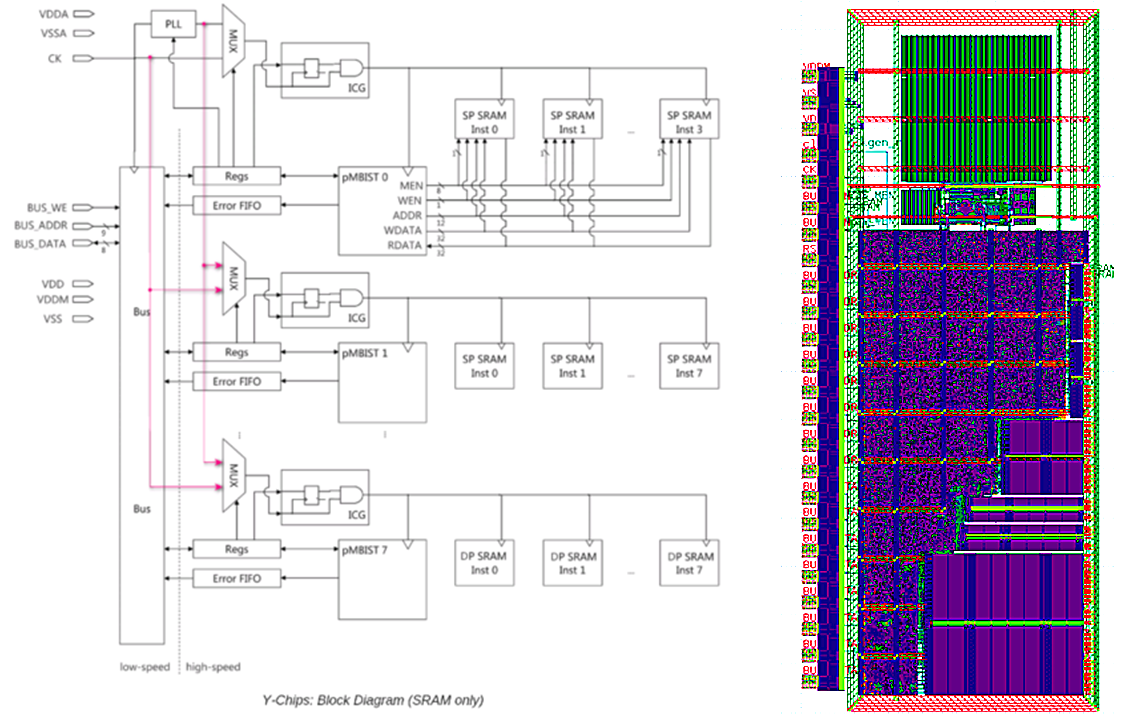

- SRAM阵列功能与速度验证:包含多类型SRAM阵列,容量充足,便于测定良率;外部搭建BIST电路,结合lib库参数实现频率性能测试。

应用案例:某工艺平台Y-CHIP验证平台

该Y-CHIP项目面向某先进工艺平台的产线导入期测试需求,具备如下特性:

功能特性

- 片上集成内建自测试(BIST),显著降低对自动测试设备(ATE)的依赖

- 集成锁相环(PLL),可支持高速性能测试

- 包含可测SRAM阵列,验证片上存储器良率

- 多个SRAM实例,满足多组阵列的测试需求

- 内建完整的标准单元库及配套测试电路

- 包含基于标准单元构建的数字功能模块

- 提供24个Pad用于功能测试和信号采样

技术优势

- 实现对新工艺平台在功能、性能、良率三方面的全面测试验证

- 支持大规模并行验证,缩短良率爬升周期

- 易于与仿真平台及ATE接口对接,便于产业化部署

国产EDA技术先驱 | 培风图南半导体

国产EDA技术先驱 | 培风图南半导体