低成本设计方案

设计思路

在数字电路设计中,业界普遍采用晶圆厂(FAB)提供的标准单元库和SRAM IP。然而,这些通用IP在面积优化方面并不总是最佳选择。针对特定设计需求,采用定制的标准单元库和替代型SRAM方案,有机会显著降低芯片面积,实现更具成本效益的布局方案。

标准单元库优化

- 传统做法:FAB提供的标准单元库通常在速度、功耗、布线便利性等多方面进行权衡设计,具有较强的通用性,但面积往往不是最小。

- 定制优化:针对特定应用场景,可根据布局密度和时序要求定制标准单元库,有望将面积进一步压缩。

- 典型成效:视具体工艺与需求,定制单元库的面积可缩减约30%以上。

- 适用场景:由于定制单元可能牺牲部分驱动能力或布线空间,通常适用于速度要求较低、布线密度不高的模块。

SRAM IP替代策略

- 问题识别:传统SRAM IP虽然单元部分采用高密度工艺设计,但外围读写电路往往沿用标准工艺,导致小容量SRAM IP面积未必优于DFF(触发器)阵列。

- DFF替代:对于8Kbit及以下容量的SRAM模块,直接使用DFF阵列替代IP可显著减小面积。

- 进一步优化:采用latch阵列代替DFF,不仅能进一步降低面积,还能通过接口逻辑模拟SRAM行为,实现平滑替换。

- 面积收益:在部分案例中,latch阵列相较DFF阵列可实现约50%的面积压缩。

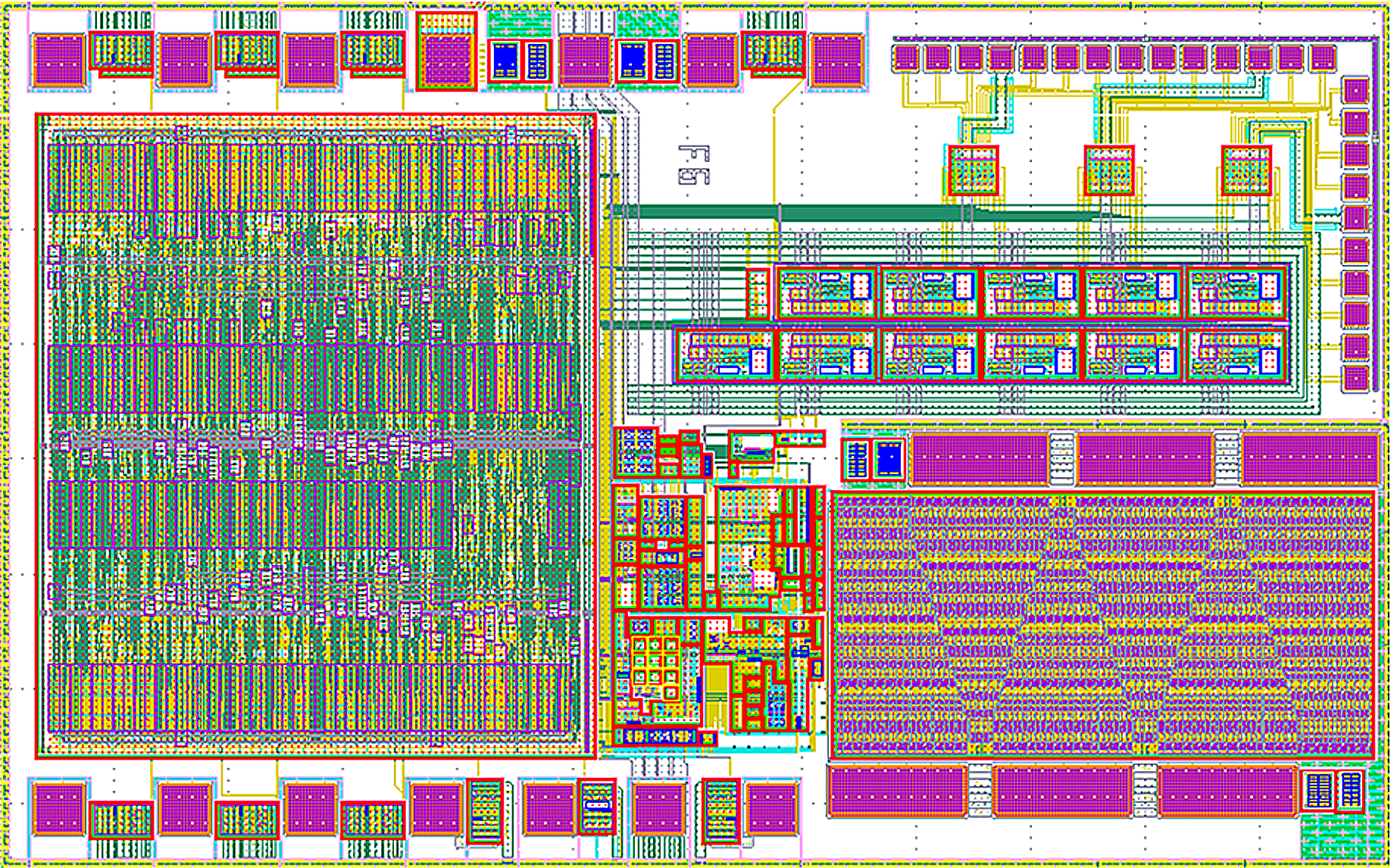

应用案例:公司内部低成本设计实践

- 标准单元库定制:针对某项目定制标准单元库,实现面积缩减约30%。

- DFF阵列替换:部分功能模块采用latch阵列替代DFF阵列,面积缩减达到约55%。

- 未使用SRAM IP:全流程采用DFF/latch阵列替代方式,避免传统SRAM IP引入的面积开销。

国产EDA技术先驱 | 培风图南半导体

国产EDA技术先驱 | 培风图南半导体