DTCO in advanced logic technologies

Advanced logic technology development (FinFET and beyond) requires the exploration of new materials and transistor structures to achieve optimal performance, power, area, cost and manufacturing yield. A major challenge in advanced technology development is to identify the best architecture as early as possible manner while covering all the possible device and process technology options.

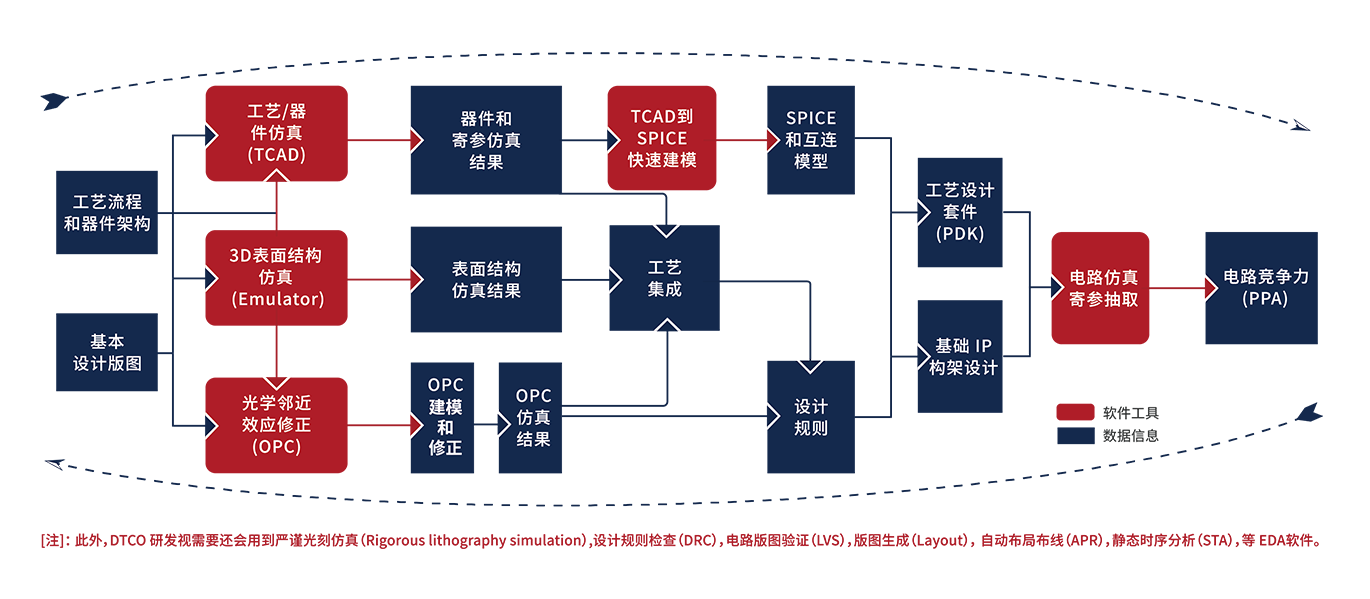

Our suite of high-fidelity process, device and lithography simulators enable evaluation of device and process options well before any wafer is available. The design connectivity tools, generate TCAD-based compact model for devices and parasitic RC netlists for circuit blocks, and further enable analyses on performance, power, area, cost and manufacturing yield metrics.

In the continuous development of advanced logic technology, DTCO (Device-Technology Co-Optimization) plays a crucial role. Especially with the emergence of FinFET and higher-level technologies, the exploration of new materials and transistor structures has become increasingly urgent in seeking the optimal balance between performance, power consumption, area, cost, and manufacturing yield. However, in the process of advancing these advanced technologies, a significant challenge lies in how to determine the optimal architecture as early as possible, while covering all possible device and process technology options comprehensively.

To address this challenge, we have introduced a high-fidelity process, device, and lithography simulator suite. This innovative tool suite enables precise evaluation of various options for devices and processes before any wafers are actually available. This not only helps us identify potential issues and bottlenecks early on but also allows targeted optimization at the design stage, significantly enhancing the performance of the final product.

Furthermore, we also use design connectivity tools to generate compact models based on TCAD (Technology Computer Aided Design). These models accurately reflect the parasitic RC network list of devices and circuit blocks, providing in-depth analysis for performance, power consumption, area, cost, and manufacturing yield. Through this approach, we can promptly identify and correct potential defects in the design process, ensuring that all indicators of the final product meet the expected goals.

In summary, our high-fidelity process, device, and lithography simulator suite, as well as the TCAD-based compact model generation tool, provide strong support for DTCO in advanced logic technology. They not only help us achieve co-optimization of devices and technologies but also drive continuous progress and development in the entire field of advanced logic technology.

Domestic EDA technology pioneer | PFTN semiconductor

Domestic EDA technology pioneer | PFTN semiconductor