Radiation Hardened Cell Library

Product Brochure

PFTN provides standard cell library development services at 130nm - 65nm technology nodes at the wafer fab of the customers' choice. A basic library includes:

-

96 combinational cell

-

24 flip-flops, including SEU/SET-hardened DICE flip-flops

-

30 digital IO cells

Additional cells can be added upon request.

Radiation Tolerance

- Total ionization dose (TID) tolerance > 300 kRad(Si)

- SEL immune with threshold LET > 90 MeV-cm2/mg.

- Static SEU rate < 10-9 #/bit/day in GEO orbit environment.

- Specialized circuit cells

- DICE flip-flops, with optinal delay-filtering for enhanced SET tolerance.

- Clock buffer with reduced SET sensitivity.

- TMR voter

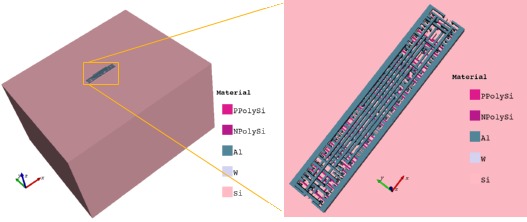

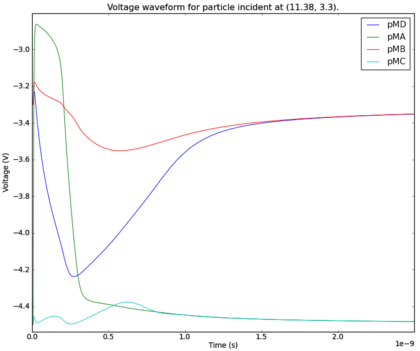

Radiation tolerance designs are verified with PFTN's fully-physical SEE simulation framework.

Fig. 1 TCAD model of a DICE flipflop used for validating the SEU-hardness of the design.

Fig. 2 TCAD simulated voltage waveform of the storage nodes in a DICE flipflop, showing prompt recovery after hit by a heavy ion.

Extensive simulations have been performed at the computing cluster at Cogenda to optimize the layout of circuit cells for SEL immunity and cross-section minimization. Through many design-simulate iterations, hardness is achieved without incurring excessive over-design.

EDA Flow

PFTN uses an in-house automation flow for cell library creation, and provides a set of vendor-neutal EDA views that can be used in the standard ASIC flow of all major EDA vendors.

| Item | Format |

|---|---|

| Functional description | Verilog |

| Netlist for LVS | CDL |

| Mask layout | GDSII |

| Synthesis library | Liberty |

| Abstract physical library | LEF |

| Symbol | EDIF |

| Place and routing rules | .tf / .lef |

PFTN can provide test chip and test keys for radiation hardness tests. A typical design cycle targets a first tape-out in six months.

Domestic EDA technology pioneer | PFTN semiconductor

Domestic EDA technology pioneer | PFTN semiconductor